在一个晶圆上,通常有几百个至数千个芯片连在一起。它们之间留有80um至150um的间隙,此间隙被称之为划片街区(Saw Street)。将每一个具有独立电气性能的芯片分离出来的过程叫做划片或切割(Dicing Saw)。目前,机械式金刚石切割是划片工艺的主流技术。在这种切割方式下,金刚石刀片(Diamond Blade)以每分钟3万转到4万转的高转速切割晶圆的街区部分,同时,承载着晶圆的工作台以一定的速度沿刀片与晶圆接触点的切线方向呈直线运动,切割晶圆产生的硅屑被去离子水(DI water)冲走。依能够切割晶圆的尺寸 ,目前半导体界主流的划片机分8英寸晶圆和12英寸晶圆划片机两种。

晶圆划片工艺的重要质量缺陷的描述

崩角 (Chipping)

因为硅材料的脆性,机械切割方式会对晶圆的正面和背面产生机械应力,结果在芯片的边缘产生正面崩角(FSC- Front Side Chipping)及背面崩角(BSC – Back Side Chipping)。

正面崩角和背面崩角会降低芯片的机械强度,初始的芯片边缘裂隙在后续的封装工艺中或在产品的使用中会进一步扩散,从而可能引起芯片断裂,导 致电性失效。另外,如果崩角进入了用于保护芯片内部电路、防止划片损伤的密封环(Seal Ring)内部时,芯片的电气性能和可靠性都会受到影响。

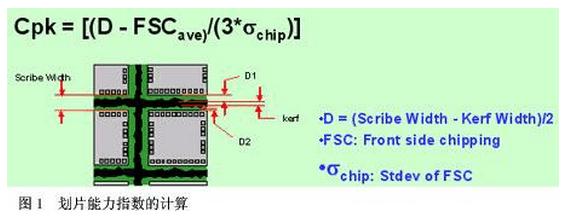

封装工艺设计规则限定崩角不能进入芯片边缘的密封圈。如果将崩角大小作为评核晶圆切割质量/能力的一个指标,则可用公式来计算晶圆切割能力指数(Cpk)(图1)。

D1、D2代表划片街区中保留完整的部分,FSC是指正面崩角的大小。依照封装工艺设计规则,D1、D2的最小值可以为0,允许崩角存在的区域宽度D为(街区宽度-刀痕宽度)/2, 为D1、D2的平均值, 为D1、D2的方差。依统计学原理,对于一个合格的划片工艺而言,其切割能力指数应大于1.5。

分层与剥离(Delamination & Peeling)

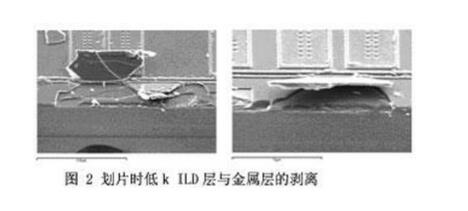

由于低k ILD层独特的材料特性,低k晶圆切割的失效模式除了崩角缺陷外,芯片边缘的金属层与ILD层的分层和剥离是另一个主要缺陷(图2)。

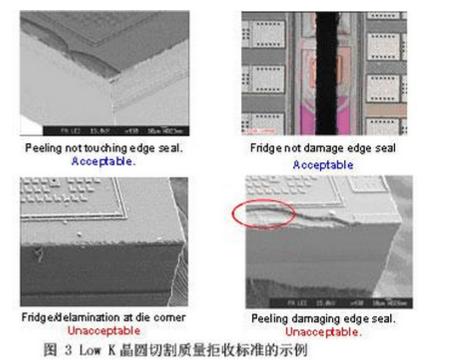

对于低k晶圆切割质量评估,除了正面崩角和背面崩角以外,根据实验数据和可靠性结果,规定了下述切割质量指标:

(1)铜密封环不允许出现断裂,分层或其他任何(在200倍显微镜下)可见的损伤。

(2)在划片街区上出现金属与ILD层的分层是允许的,只要这种分层能止步于铜密封环外。

(3)在芯片的顶角区域的金属/ILD层不允许出现分层或损伤,唯一的例外是有封装可靠性数据证明在某种特定的芯片设计/封装结构的组合下芯片的顶角区域的损伤可以接受。

图3给出了低k晶圆切割质量拒收标准的示例。

影响晶圆划片质量的重要因素

划片工具,材料及划片参数

划片工具和材料主要包括:划片刀(Dicing blade)、承载薄膜(Mounting tape), 划片参数主要包括:切割模式、切割参数(步进速度、刀片转速、切割深度等)。对于由不同的半导体工艺制作的晶圆需要进行划片工具的选择和参数的优化,以达到最佳的切割质量和最低的切割成本。

切割街区的测试图案

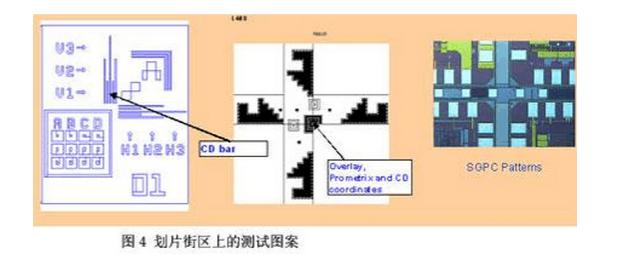

在晶圆的制造过程中,为了获得较高的成品率、较低的制造成本和稳定的工艺制程,每一步工艺都处于严格的监控下。因此,测试

图案被设计出来并对其进行监测,以确保关键参数如电参数、制程精度如ILD层/金属层的淀积厚度、掩膜对准精度及金属线宽容差等满足设计要求。通常有3种方式来实现晶圆工艺制程监控:

(1)离线测试,这种测试将所有的测试图案放入被称为―工艺确认晶圆‖(PVW – Process Validation Wafer)的特别设计的晶圆上。优点是可以包括所有需要测试的图案,因而可以执行一个全面的工艺制程监控;缺点是高成本和费时。它通常应用在产品的研发初期。当产品技术日趋成熟后,这种测试方法会被其他的测试方法所取代。

(2)测试芯片插入法。所有的测试图案被放入测试芯片内,这些测试芯片被安放在晶圆上的不同区域。测试芯片的数目和位置取决于晶圆制造技术的复杂度。优点是它是一种实时监控。如果某种致命的缺陷发生在晶圆制造流程的早期,就可以避免由于整个晶圆报废而带来的损失。这种测试方法的缺点是它占用了宝贵的硅片资源,尤其是当单个芯片尺寸较大,而PDPW(Potential Die Per Wafer)数目较小的时候。

(3)周边测试,测试图案被放置在划片街区内(图4)。将测试图案放在划片街区内能够在实现实时监控的同时,节约了宝贵的硅片资源。可以放进划片街区的测试图案的数目取决于在一个掩膜(Reticle)内划片街区的长度和面积。在一个Reticle内划片街区上的测试图案,会随着步进式光刻的进行,在整个晶圆上得到复制。在Reticle内部,所有的测试图案都是唯一的,互不相同。而在不同的Reticle之间,测试图案是重复的。